## MLPF-WB and MLPF-NRG PCB design guidelines and reference hardware

### Introduction

RF filters are critical components for wireless communication.

These filters ensure a robust and clean RF signal, enabling long-range and high-quality RF links.

To address this need, ST provides a comprehensive portfolio of companion chip filters specifically designed for each wireless STM32W microcontroller.

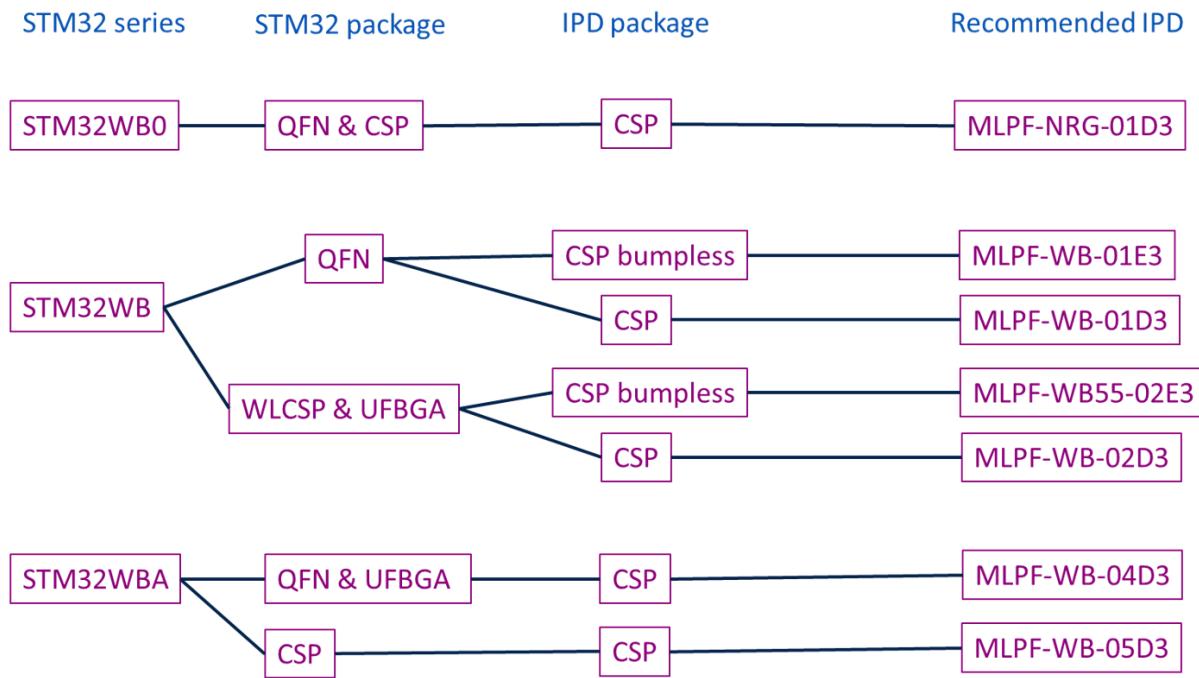

The Figure 1 presents the IPD filter selection tree based on the STM32 series, STM32 package, and IPD package.

Figure 1. IPD filter selection tree

The following pages provide the MLPF-WB and MLPF-NRG PCB design guidelines and reference hardware.

## 1 MLPF-NRG-01D3:

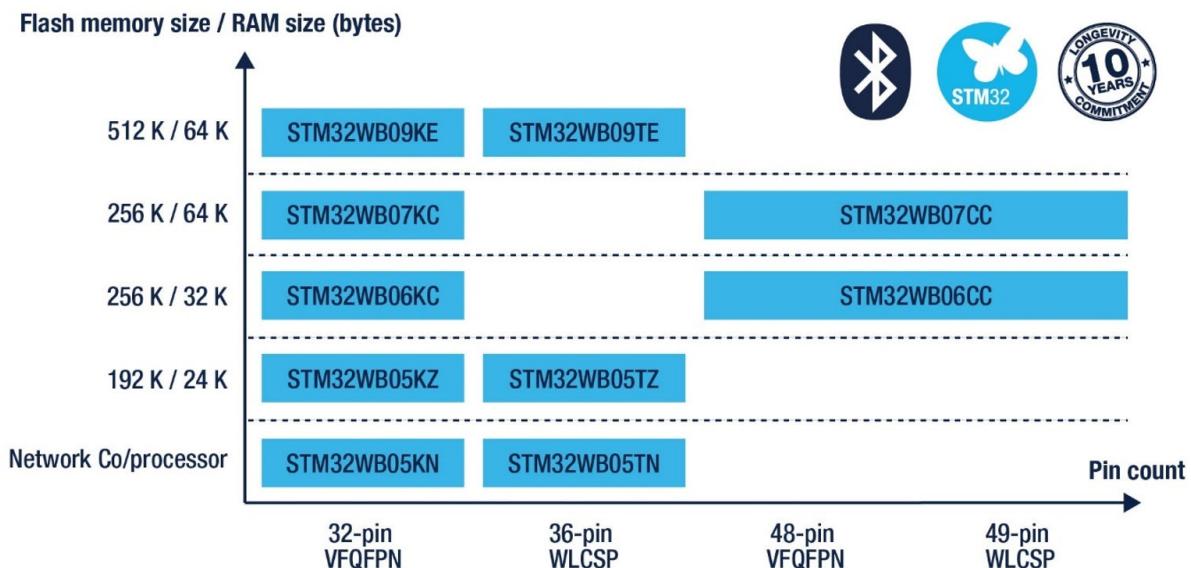

The STM32WB0 microcontroller series enables reliable wireless performance in a compact, energy-efficient design.

Based on the Arm Cortex®-M0+ core running at 64 MHz, the series offers up to 512 KB of flash memory and 64 KB of RAM.

Certified for Bluetooth® LE 5.4, the STM32WB0 achieves best-in-class power consumption, making it ideal for cost-sensitive and energy-sensitive wireless applications.

Figure 2. STM32WB0 microcontroller series

The MLPF-NRG-01D3 simplifies the implementation of the STM32WB0 series.

The MLPF-NRG-01D3 is compatible with the STM32WB0 in both QFN and CSP packages. It ensures compliance with all standard levels while providing proper impedance matching to maximize the output power level.

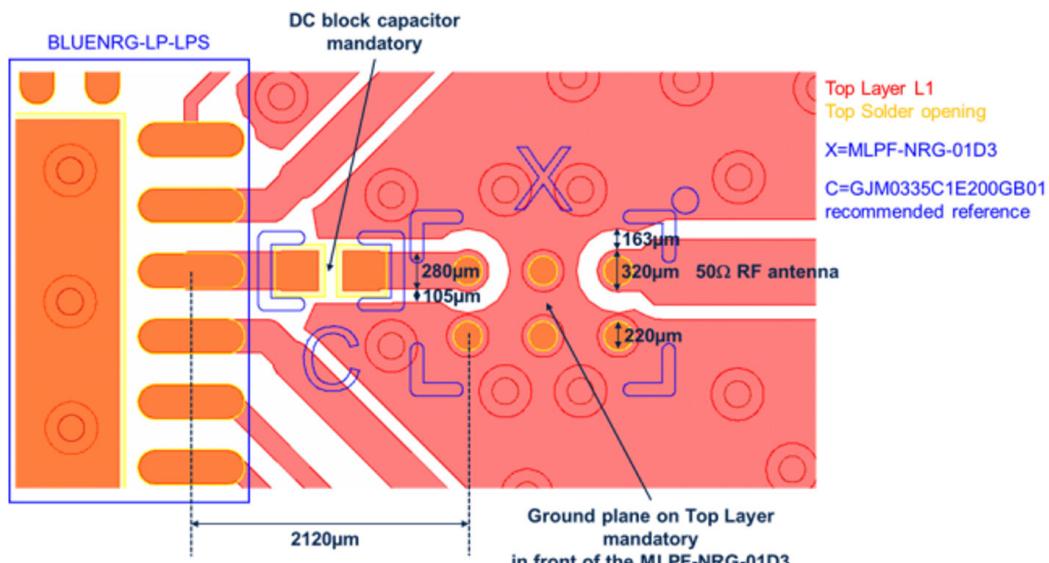

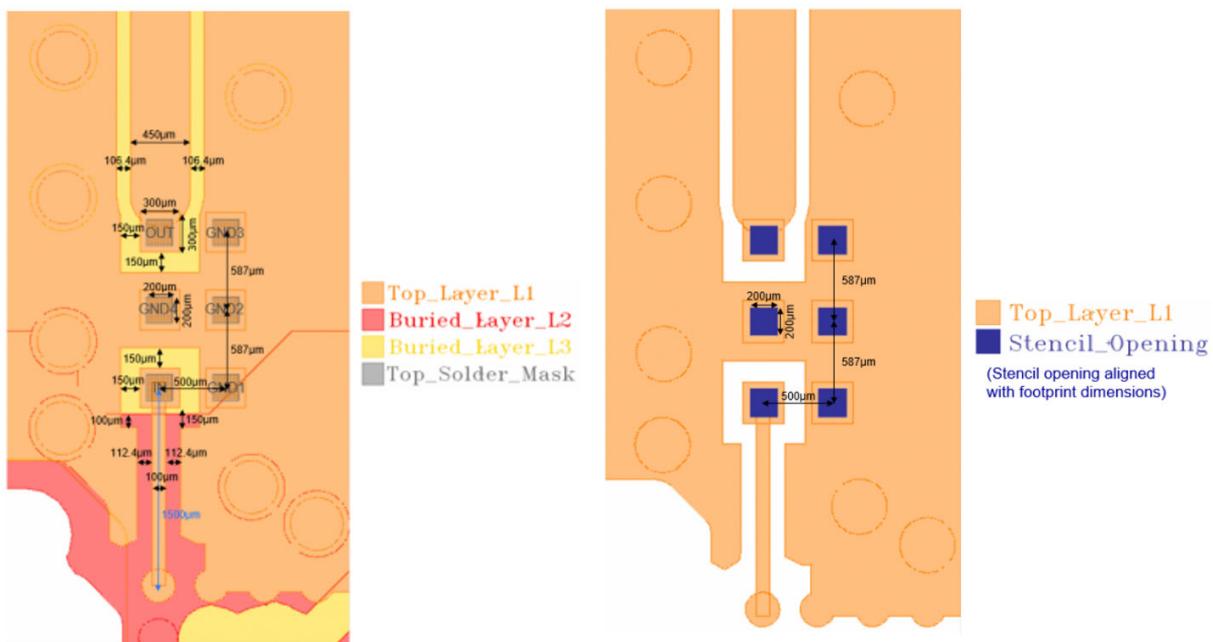

The MLPF-NRG-01D3 datasheet provides layout information, as shown in the Figure 3:

Figure 3. MLPF-NRG-01D3 layout

The transmission line between the MLPF and the antenna must have a  $50\ \Omega$  characteristic impedance.

The transmission line between the STM32 and the MLPF must have a  $57\ \Omega$  characteristic impedance.

Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

The drill density must be maximized near the **MLPF-NRG-01D3** area to ensure optimal RF performance.

From an assembly perspective, the solder mask-defined approach must be followed to ensure the correct assembly height.

Reference design resources for the MLPF-NRG-01D3 are available on [www.st.com](http://www.st.com) with the **NUCLEO-WB09KE** and **X-NUCLEO-WB05KN1**.

**Figure 4. NUCLEO-WB09KE and X-NUCLEO-WB05KN1 views**

## 2

## MLPF-WB-01E3:

STM32WB series is based on dual-core, multiprotocol wireless STM32WB microcontrollers that support Bluetooth® LE, Zigbee®, Thread®, and matter connectivity.

The STM32WB wireless microcontroller is a self-sufficient solution that integrates connectivity features and a general-purpose microcontroller in a single system-on-chip (SoC). It is based on an Arm Cortex®-M4 core running at 64 MHz (application processor) and an Arm Cortex®-M0+ core running at 32 MHz (network processor).

Figure 5. STM32WB MCU series

| RADIO                              | Product line | ICPU (MHz) | Flash (byte) | RAM (byte) | Modulations     |         |               |               | OTA | External PA capable | HW Security | Customer Key Storage | ADC | 16-bit HW oS | Quad-SPI | USB 2.0 FS (crystal less) | SAI | Segment LCD driver | Operating temperature range   |

|------------------------------------|--------------|------------|--------------|------------|-----------------|---------|---------------|---------------|-----|---------------------|-------------|----------------------|-----|--------------|----------|---------------------------|-----|--------------------|-------------------------------|

|                                    |              |            |              |            | Concurrent mode | BLE 5.4 | IEEE 802.15.4 | IEEE 802.15.4 |     |                     |             |                      |     |              |          |                           |     |                    |                               |

| Cortex-M4 and -M0+ dual core lines |              |            |              |            |                 |         |               |               |     |                     |             |                      |     |              |          |                           |     |                    |                               |

|                                    | STM32WB55    | Up to 64   | 256K to 1M   | Up to 256K | •               | •       | •             | •             | •   | •                   | •           | •                    | •   | •            | •        | •                         | 2   | Up to 8x40         | -40° to 85°C<br>-40° to 105°C |

|                                    | STM32WB35    | Up to 64   | 256 to 512K  | 96K        |                 | •       | •             | •             | •   | •                   | •           | •                    | •   | •            | •        | •                         | 2   |                    | -40° to 85°C<br>-40° to 105°C |

|                                    | STM32WB15    | Up to 64   | 320K         | 48K        |                 | •       |               | •             | •   | •                   |             |                      |     |              |          |                           |     |                    | -40° to 85°C<br>-40° to 105°C |

| Value lines                        |              |            |              |            |                 |         |               |               |     |                     |             |                      |     |              |          |                           |     |                    |                               |

|                                    | STM32WB50    | Up to 64   | 1M           | 128K       |                 | •       | •             | •             |     | •                   |             |                      |     |              |          |                           |     |                    | -10° to 85°C                  |

|                                    | STM32WB30    | Up to 64   | 512K         | 96K        |                 | •       | •             | •             |     | •                   |             |                      |     |              |          |                           |     |                    | -10° to 85°C                  |

|                                    | STM32WB10    | Up to 64   | 320K         | 48K        |                 | •       |               | •             |     | •                   |             |                      |     |              |          |                           |     |                    | -10° to 85°C                  |

The MLPF-WB-01E3 is compatible with the STM32WB series in the QFN package (for example, STM32WB55Cx, STM32WB55Rx, STM32WB50Cx, STM32WB35Cx, STM32WB30Cx). It ensures compliance with all standard levels and provides proper impedance matching to maximize the output power level.

The MLPF-WB-01E3 is a CSP bumpless component with an LGA footprint.

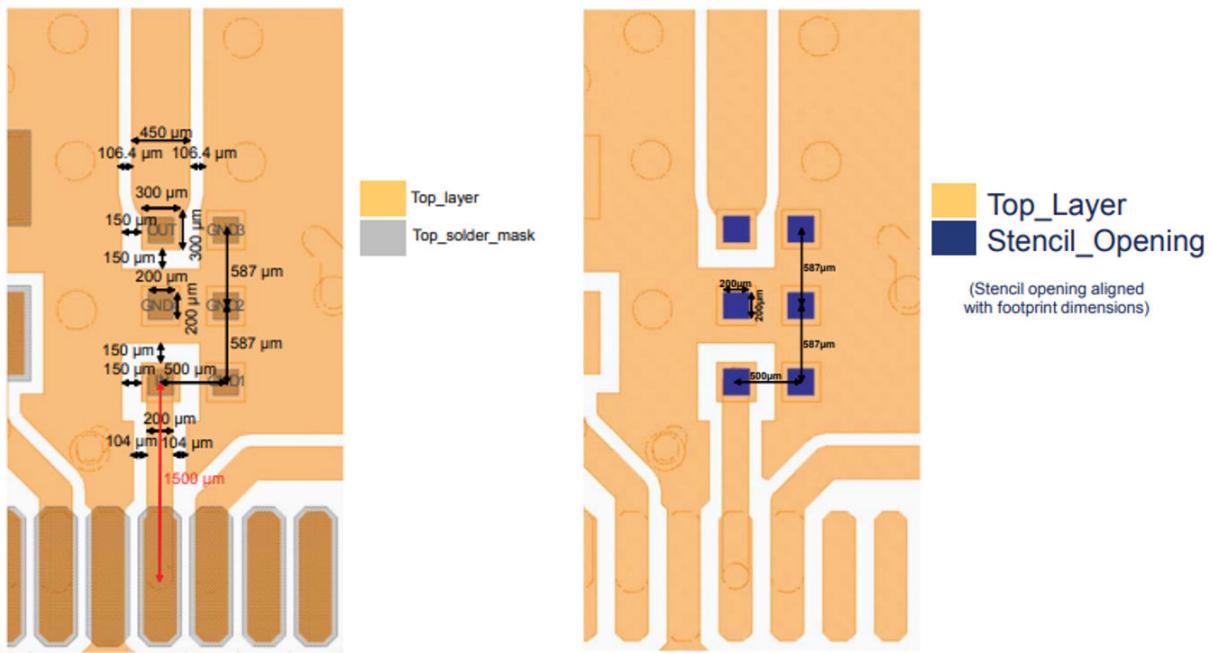

The **MLPF-WB-01E3** datasheet provides layout information, as shown in the **Figure 6** below:

**Figure 6. MLPF-WB-01E3 layout**

The transmission line between the MLFP and the antenna is designed for a  $50 \Omega$  characteristic impedance.

The transmission line between the STM32 and the MLPF is designed for a  $62 \Omega$  characteristic impedance.

Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

From an assembly perspective, a solder mask-defined approach must be followed to ensure the correct assembly height.

Reference design resources for the MLPF-WB-01E3 are available on [www.st.com](http://www.st.com) with the NUCLEO-WB55RG.

Figure 7. MLPF-WB-01E 3D view

### 3 MLPF-WB55-02E3:

The MLPF-WB55-02E3 is compatible with the STM32WB series in WLCSP and UFBGA packages, such as STM32WB55Vx. It complies with all standard levels and ensures proper impedance matching to maximize the output power level.

The MLPF-WB55-02E3 is a CSP bumpless component with an LGA footprint.

The MLPF-WB55-02E3 datasheet provides layout information, as shown in the Figure 8 below:

Figure 8. MLPF-WB55-02E3 layout

The transmission line between the MLPF and the antenna is designed for a  $50 \Omega$  characteristic impedance.

The transmission line between the STM32 and the MLPF is designed for a  $56 \Omega$  characteristic impedance.

Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

From an assembly perspective, the solder mask-defined approach must be followed to ensure the correct assembly height.

## 4 MLPF-WB-01D3:

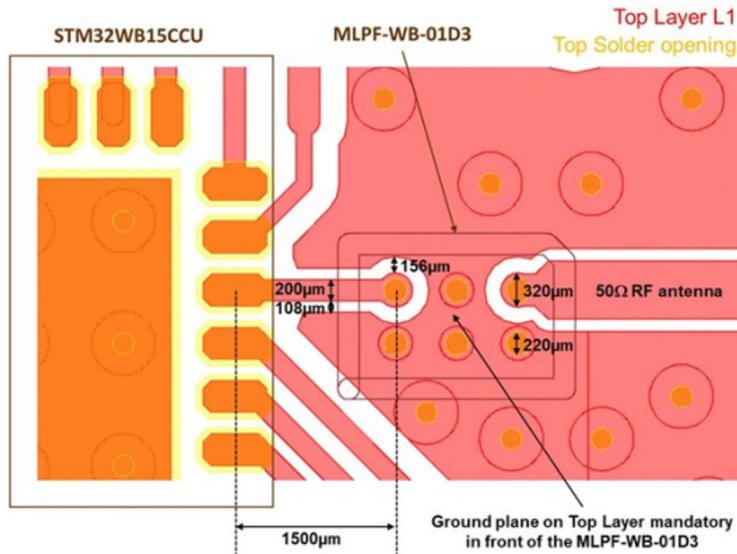

The [MLPF-WB-01D3](#) is compatible with the STM32WB series in UFQFPN and VFQFPN packages. It complies with all standard levels and provides proper impedance matching to maximize the output power level.

The [MLPF-WB-01D3](#) datasheet provides layout information, as shown in the [Figure 9](#) below. Refer to the datasheet at [MLPF-WB-01D3](#).

**Figure 9. MLPF-WB-01D3 layout**

The transmission line between the MLPF and the antenna is designed for a  $50\ \Omega$  characteristic impedance.

The transmission line between the STM32 and the MLPF is designed for a  $67\ \Omega$  characteristic impedance.

Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

The drill density must be maximized near the [MLPF-WB-01D3](#) area to ensure optimal RF performance.

From an assembly perspective, a solder mask-defined approach must be followed to ensure the correct assembly height.

Reference design resources for the [MLPF-WB-01D3](#) are available on [www.st.com](http://www.st.com) for the [MLPF-WB-01D3](#) with the [NUCLEO-WB05KZ](#).

**Figure 10. MLPF-WB-01D3 3D view**

## 5 MLPF-WB-02D3:

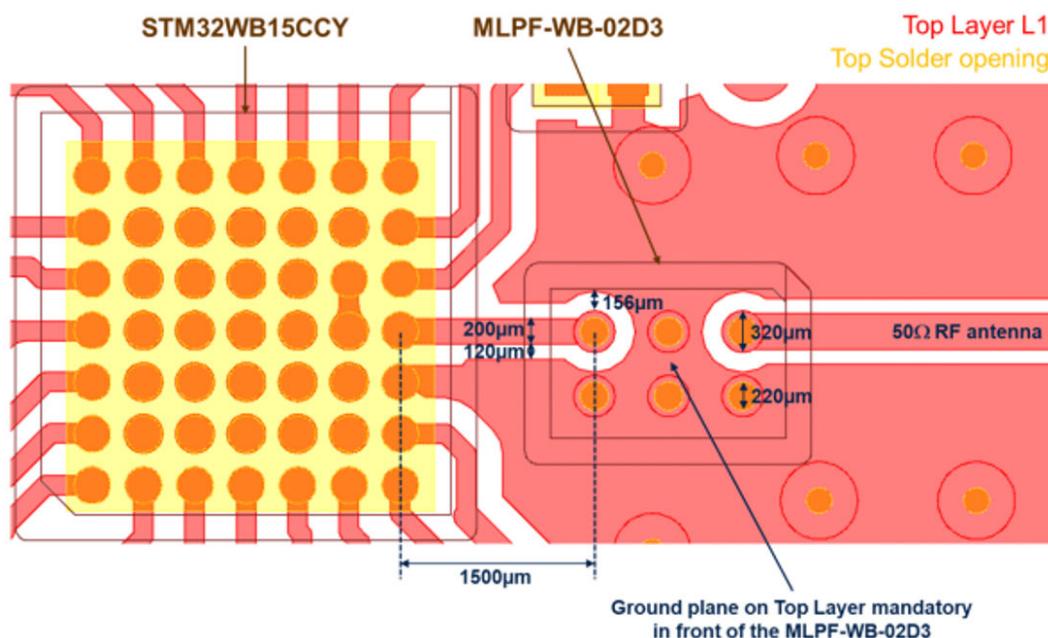

The MLPF-WB-02D3 is compatible with the STM32WB series in WLCSP and UFBGA packages, such as STM32WB5x and STM32WB1x. It ensures compliance with all standard levels while providing proper impedance matching to maximize the output power level.

The MLPF-WB-02D3 datasheet includes layout information, as illustrated in the Figure 11 below:

Figure 11. MLPF-WB-02D3 layout

The transmission line between the MLPF and the antenna is designed for a  $50\ \Omega$  characteristic impedance.

The transmission line between the STM32 and the MLPF is designed for a  $61\ \Omega$  characteristic impedance.

Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

The drill density near the MLPF-WB-02D3 area must be maximized to ensure optimal RF performance.

From an assembly perspective, a solder mask-defined approach must be followed to ensure the correct assembly height.

## 6 MLPF-WB-04D3:

The STM32WBA MCU series offers designers performance, efficiency, and flexibility. It integrates large memory to support both applications and connectivity activities, featuring up to 2 Mbytes of flash memory and up to 512 Kbytes of RAM. A comprehensive set of peripherals, such as ADC, touch sensing, and timers, makes this product a self-sufficient wireless MCU for applications.

Key features include:

- High data rate: Ensures fast and reliable data transfer.

- Multiprotocol flexibility: Supports Bluetooth® LE 5.4, IEEE 802.15.4 communication protocols, Zigbee®, thread, and matter.

- Long-range capability: Extends communication range.

- High output power: Increases communication range with +10 dBm of output power.

- Low-power messaging capability: Extends battery lifetime.

Based on the Arm Cortex®-M33 core running at 100 MHz with TrustZone® technology, the STM32WBA series provides a high level of security, protecting data, intellectual property, and preventing hacks or device cloning.

Portfolio example of the STM32WBA65 family:

Figure 12. STM32WBA65 family

The MLPF-WB-04D3 has been developed to simplify the implementation of the STM32WBA series. It is compatible with STM32WBA in both QFN and BGA packages. The MLPF-WB-04D3 ensures compliance with all standard levels while providing proper impedance matching to maximize output power levels.

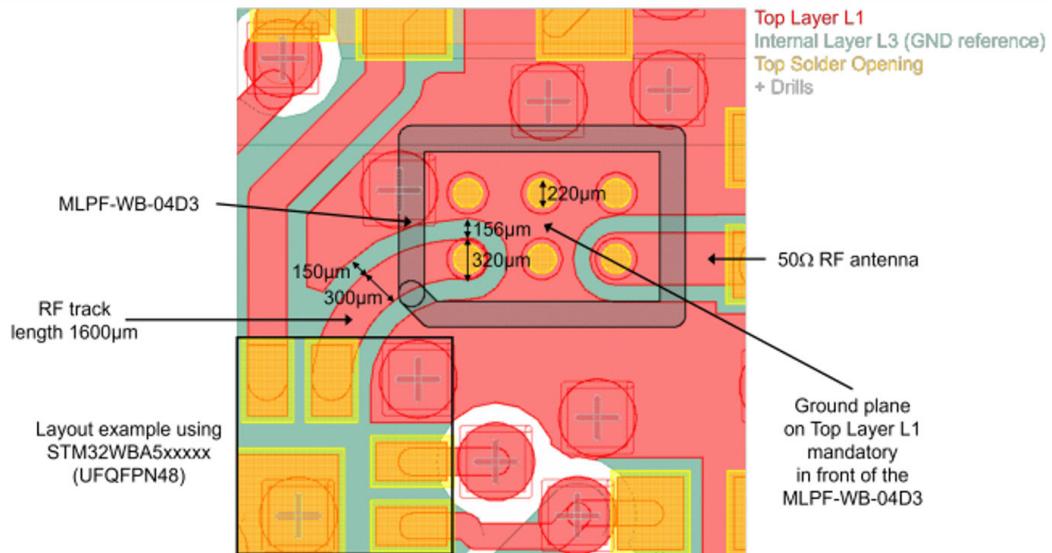

The MLPF-WB-04D3 datasheet provides layout information, as shown in the figure below:

Figure 13. MLPF-WB-04D3 layout

The RF transmission line between the MLPF and the antenna is designed for a  $50\ \Omega$  characteristic impedance. The RF transmission line between the STM32 and the MLPF is designed for a  $63\ \Omega$  characteristic impedance. Transmission line impedances and lengths must be precisely maintained. Adjust the physical line dimensions based on the actual PCB stack-up to ensure that the characteristic impedance aligns with the datasheet specifications.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

The drill density near the MLPF-WB-04D3 area must be maximized to ensure optimal RF performance.

From an assembly perspective, a solder mask-defined approach must be followed to ensure the correct assembly height.

Reference design resources for the MLPF-WB-04D3 are available on [www.st.com](http://www.st.com) with NUCLEO-WBA65RI and STM32WBA65RI.

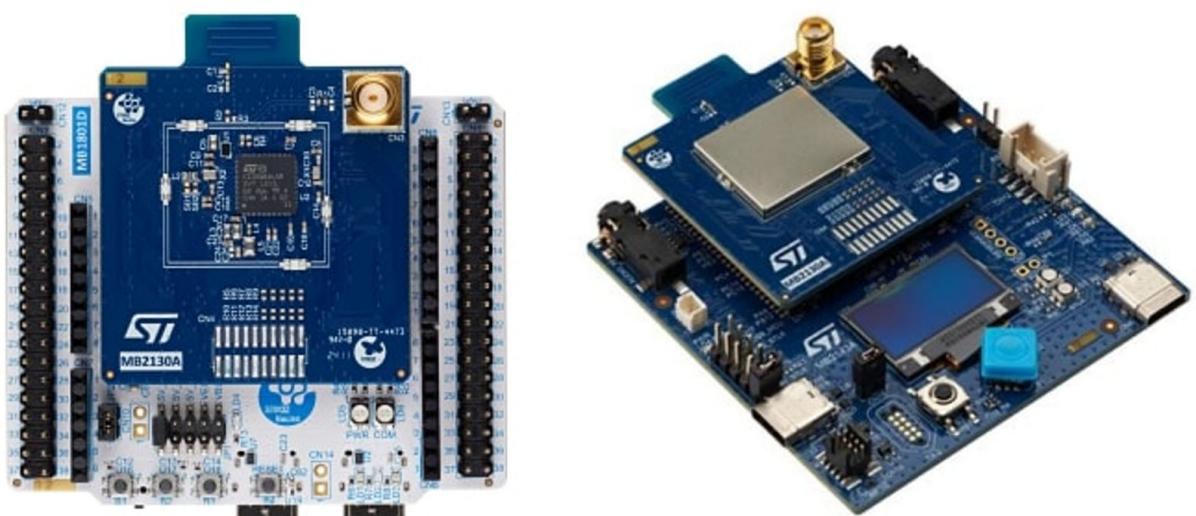

Figure 14. 3D view

## 7

## MLPF-WB-05D3:

The [MLPF-WB-05D3](#) is compatible with STM32WBA in CSP package. It complies with all standard levels and provides proper impedance matching to maximize the output power level.

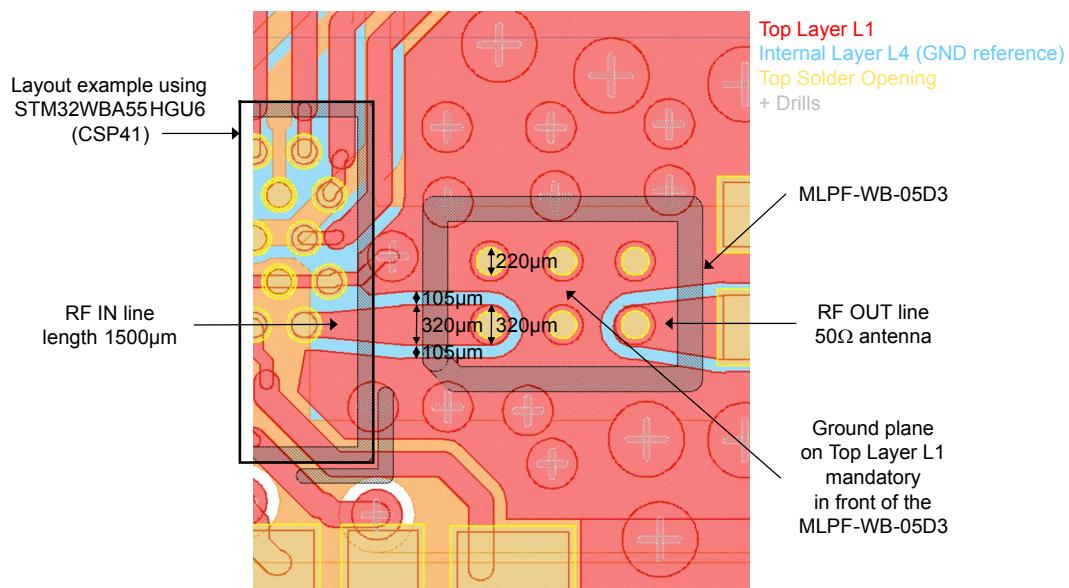

The [MLPF-WB-05D3](#) datasheet includes layout information, as illustrated in the [Figure 15](#) below:

**Figure 15. MLPF-WB-05D3 layout**

The RF IN transmission line between STM32 and MLPF is dimensioned to 55  $\Omega$  characteristic impedance.

This characteristic impedance has to be followed as close as possible, within a tolerance of  $\pm 15\%$ .

The length of the RF IN line must be followed as precisely as possible.

The RF OUT transmission line between MLPF and antenna is dimensioned to 50  $\Omega$  characteristic impedance.

The ground plane on top layer is mandatory in front of the [MLPF-WB-05D3](#), with its geometries which allow the best equipotentiality.

The drill density near the [MLPF-WB-05D3](#) area must be maximized to ensure optimal RF performance.

Special attention must be given to the clearance around the IN and OUT pads of the MLPF to achieve optimal RF performance.

From an assembly perspective, a solder mask-defined approach must be followed to ensure the correct assembly height.

## Revision history

**Table 1. Document revision history**

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 01-Aug-2025 | 1        | Initial release. |

## Contents

|          |                         |           |

|----------|-------------------------|-----------|

| <b>1</b> | <b>MLPF-NRG-01D3:</b>   | <b>2</b>  |

| <b>2</b> | <b>MLPF-WB-01E3:</b>    | <b>4</b>  |

| <b>3</b> | <b>MLPF-WB55-02E3:</b>  | <b>7</b>  |

| <b>4</b> | <b>MLPF-WB-01D3:</b>    | <b>8</b>  |

| <b>5</b> | <b>MLPF-WB-02D3:</b>    | <b>10</b> |

| <b>6</b> | <b>MLPF-WB-04D3:</b>    | <b>11</b> |

| <b>7</b> | <b>MLPF-WB-05D3:</b>    | <b>13</b> |

|          | <b>Revision history</b> | <b>14</b> |

|          | <b>List of tables</b>   | <b>16</b> |

|          | <b>List of figures</b>  | <b>17</b> |

## List of tables

|                                              |    |

|----------------------------------------------|----|

| Table 1. Document revision history . . . . . | 14 |

|----------------------------------------------|----|

## List of figures

|                   |                                          |    |

|-------------------|------------------------------------------|----|

| <b>Figure 1.</b>  | IPD filter selection tree.               | 1  |

| <b>Figure 2.</b>  | STM32WB0 microcontroller series          | 2  |

| <b>Figure 3.</b>  | MLPF-NRG-01D3 layout                     | 2  |

| <b>Figure 4.</b>  | NUCLEO-WB09KE and X-NUCLEO-WB05KN1 views | 3  |

| <b>Figure 5.</b>  | STM32WB MCU series                       | 4  |

| <b>Figure 6.</b>  | MLPF-WB-01E3 layout                      | 5  |

| <b>Figure 7.</b>  | MLPF-WB-01E 3D view                      | 6  |

| <b>Figure 8.</b>  | MLPF-WB55-02E3 layout                    | 7  |

| <b>Figure 9.</b>  | MLPF-WB-01D3 layout                      | 8  |

| <b>Figure 10.</b> | MLPF-WB-01D3 3D view                     | 9  |

| <b>Figure 11.</b> | MLPF-WB-02D3 layout                      | 10 |

| <b>Figure 12.</b> | STM32WBA65 family                        | 11 |

| <b>Figure 13.</b> | MLPF-WB-04D3 layout                      | 12 |

| <b>Figure 14.</b> | 3D view                                  | 12 |

| <b>Figure 15.</b> | MLPF-WB-05D3 layout                      | 13 |

**IMPORTANT NOTICE – READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to [www.st.com/trademarks](http://www.st.com/trademarks). All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved